AI和ML如何优化EDA的功能验证

功能验证可确保半导体设计的寄存器传输层 (RTL)实现按照指定要求运行。电子工程师通常使用SystemVerilog等硬件验证语言 (HVL)结合通用验证方法 (UVM)进行功能验证。其他 HVL,例如VHSIC 硬件描述语言 (VHDL)和属性规范语言 (PSL),可用于特定应用。

本文讨论了人工智能 (AI)和机器学习 (ML)如何加速形式验证过程,包括覆盖率、调试和回归。它还强调了大型语言模型 (LLM)在电子设计自动化 (EDA)工作流程中的扩展功能,并探讨了使用卷积神经网络 (CNN)架构进行功能验证的进步。最后,本文回顾了将 AI 驱动的工具集成到验证工作流程中面临的各种挑战。

加速覆盖、调试和回归

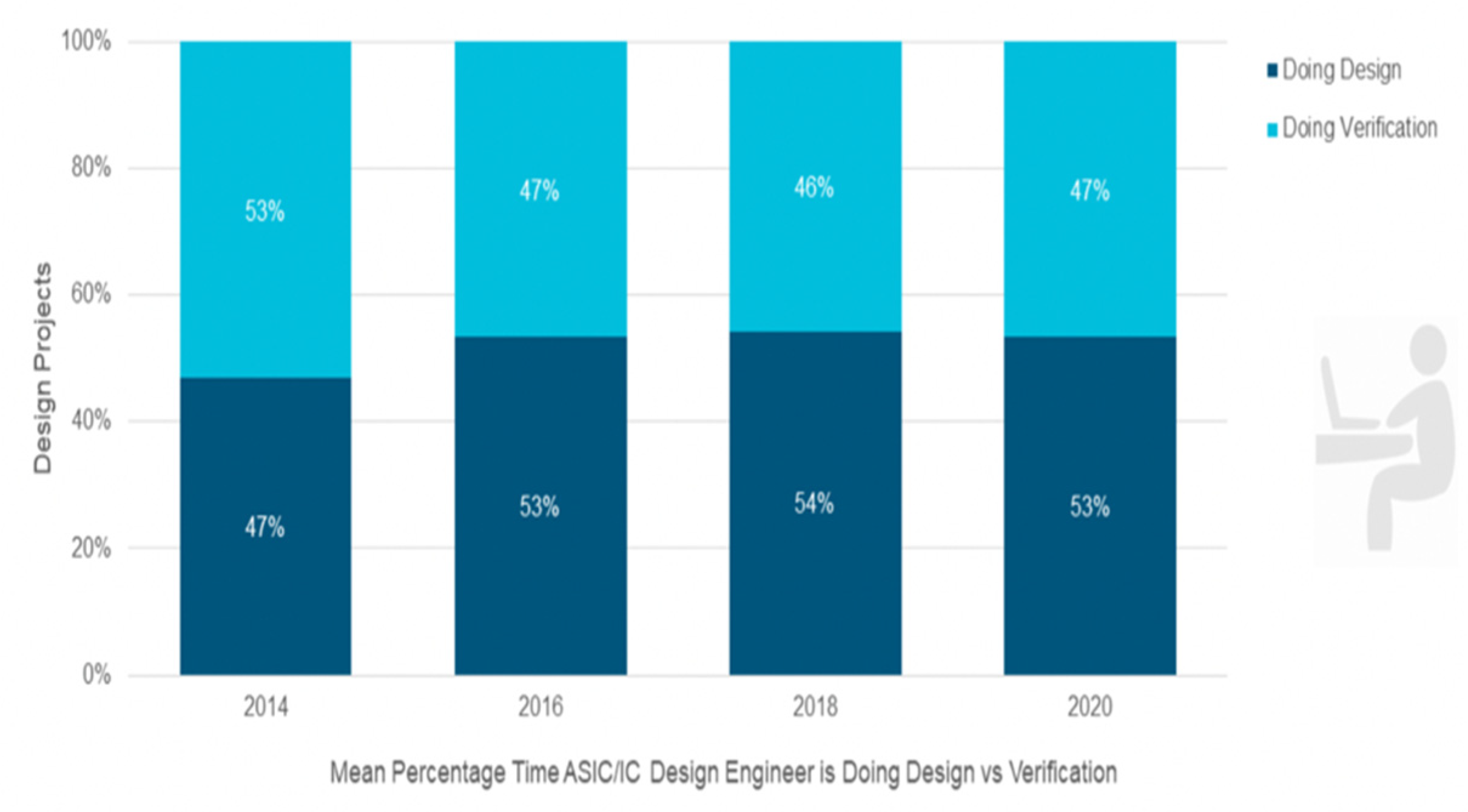

如图 1所示,功能验证是一个耗时的过程。工程师必须分析文档、制定验证计划、构建验证环境、执行定义的测试并实现完整的测试覆盖。

图 1. ASIC/IC 设计工程师在设计任务上花费的时间与验证任务上花费的时间平均百分比,突显出 2014 年至 2020 年间向验证的稳步转变。来源:MDPI

包括大型语言模型 (LLM) 在内的 AI 和 ML 技术可以通过自动化或加速各种关键任务来显著优化功能验证工作流程,例如:

· 将自然语言规范转换为SystemVerilog 断言 (SVA)或其他验证语言——在典型设计条件下实现 9.29% 的成功率,在最佳场景中实现 80% 的准确率。

· 直接从设计规范生成验证代码并生成Verilog代码,成功率从 59.9% 到 98.7% 不等,具体取决于复杂程度。

· 使用先进的 ML 算法生成测试刺激——对简单设计实现高达 98.94% 的覆盖率,对更复杂设计实现高达 86.19% 的覆盖率。

· 预测代码覆盖率在行级的准确率为 20-30%,在语句级的准确率为 84-90%。

· 自动化并加快形式化证明引擎的选择和实施。

· 分析失败的测试报告以重现 33.5% 的报告错误,简化调试工作流程并加快根本原因分析。

· 自动识别高优先级测试用例并预测故障场景以显著提高回归效率。

在 EDA 工作流程中扩展 LLM 功能

商业和开源 LLM 的最新进展优化了 EDA 工作流程,使其超越功能验证,涵盖前端、后端和生产测试阶段。这些模型可自动执行关键任务,例如代码生成、响应工程查询以及协助文档编制(包括报告生成和错误分类)。另一个关键应用是自动化脚本生成,以集成 EDA 工具、参考方法和专有逻辑。

Code Llama等基础模型擅长生成Python 脚本,并且可以针对其他脚本语言(例如Perl和Tcl)进行微调,这些语言广泛用于基于 GUI 的 EDA 工具。通过使 AI 驱动的工程助理能够创建和解释脚本并促进自然语言交互,LLM 弥合了工程师和设计界面之间的差距。此功能可优化效率,同时解决芯片设计工作流程日益复杂的问题。

利用 CNN 架构推进功能验证

为了进一步优化功能验证,研究人员最近开发了两种卷积神经网络 (CNN) 架构,可高效地对不同文档中的信息进行分类。这些模型在Anaconda环境中的10 核GPU的Apple M1硬件上进行了测试,使用自定义数据集并增强了同义词替换功能,以增强多样性和稳健性。

第一个 CNN 架构采用顺序模型,该模型由一个嵌入层、两个卷积层、两个使用整流线性单元 (ReLU) 函数的激活层、一个 MaxPooling 层、一个 Flatten 层和一个密集层组成。该模型实现了高测试准确率 (98.33%)、稳健的精度、召回率和 F1 分数以及低验证损失 (10.25%)。尽管研究人员计划使用超参数调整进一步完善该模型,但这些结果凸显了其在功能验证过程中对文档分类的可靠性和有效性。

第二个 CNN 架构在第一个 CNN 架构的基础上添加了第三个卷积层来提高性能。

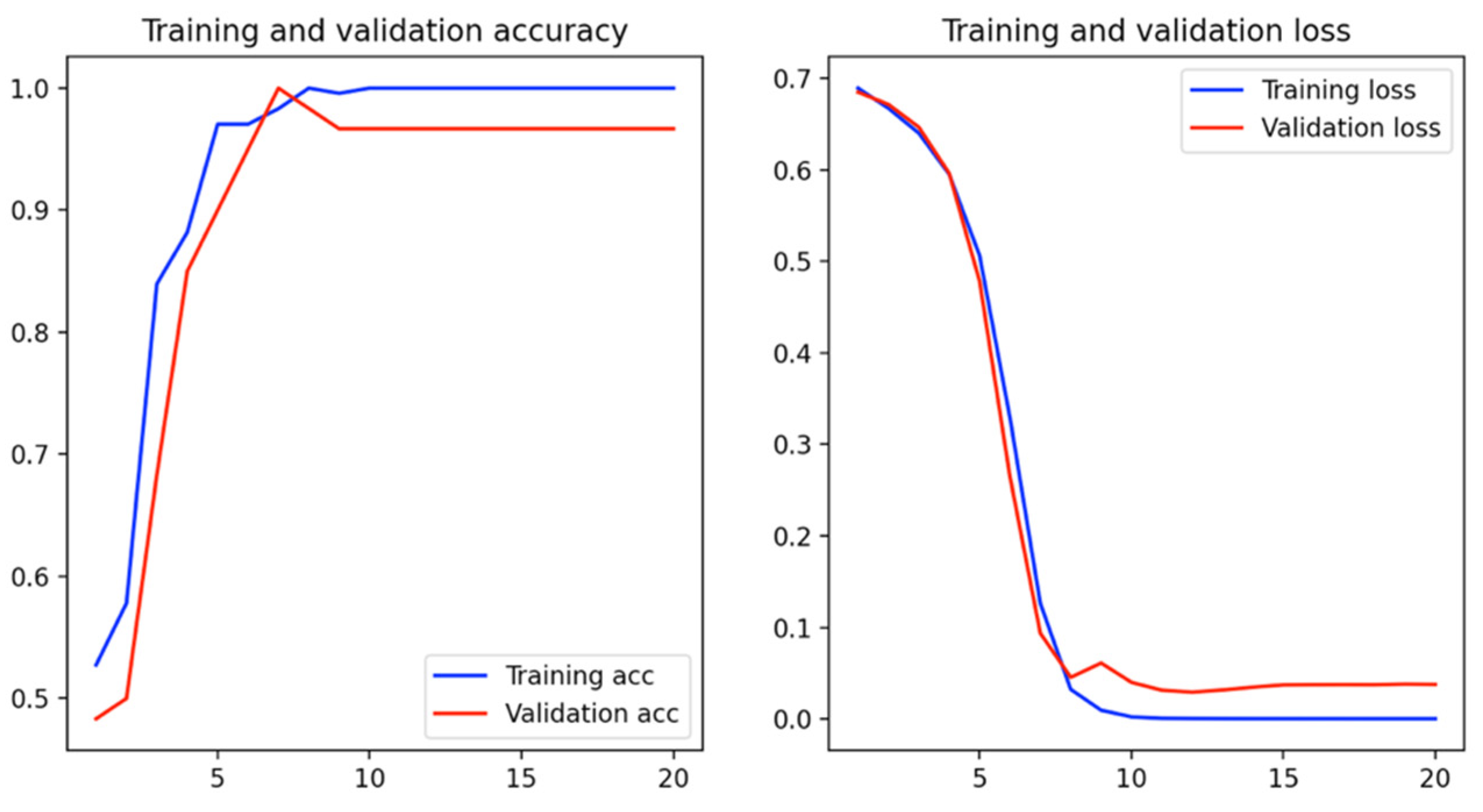

图 2. 具有三个卷积层的第二个 CNN 模型的训练和验证准确率和损失曲线,在功能验证文档分类任务中表现出低验证损失和高精度的稳健性能。来源:MDPI

它保持了类似的顺序结构,包括三个卷积层、三个激活层以及相同的嵌入层、MaxPooling、Flatten 和密集层。如图2所示,该模型的验证准确率达到 96.67%,具有良好的精度、召回率和 F1 分数,验证损失甚至更低(-5%)。

克服人工智能驱动的功能验证中的挑战

将 AI 和 ML 集成到功能验证工作流程中并非没有挑战。例如,开源 硬件描述语言 (HDL)数据集的稀缺限制了模型训练,并可能导致预测过程中出现不准确或幻觉。此外,在较小、较简单的半导体设计上表现良好的模型在应用于复杂的大型项目时往往难以保持效率和准确性。

确保跨硬件架构的泛化对于电子工程师来说是一项重大挑战,因为在特定数据集上训练的 ML 模型通常需要大量微调和再训练。此外,将 AI 和 ML 集成到验证工作流程中可能需要升级计算资源以处理大型数据集或重新设计工作流程以支持 AI 驱动的工具。

尽管面临各种挑战,但基于机器学习的 EDA 形式验证工具已取得显著改进,一些供应商报告称速度提高了 10 倍。使用基于机器学习的聚类和根本原因分析 (RCA) ,这些工具可以在典型的芯片项目周期中为静态验证提供高达 10 倍的调试效率提升。

功能验证是一个耗时的过程,涉及多个步骤,例如分析文档、构建验证环境和执行定义的测试。AI 和 ML 技术(包括 LLM 和 CNN)可以显著加速功能验证工作流程并优化前端、后端和生产测试阶段。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。