DRAM技术竞速,存储巨头策略分化

在半导体存储领域,DRAM技术的迭代始终是推动行业变革的核心动力。2025年4月,三星电子宣布成立专项工作组,全力推进第七代DRAM的量产计划。这一战略举措不仅标志着三星在先进制程领域的持续投入,更被视为打破当前高带宽内存(HBM)市场平衡的关键转折点。与此同时,SK海力士与美光在第六代DRAM技术上的快速突破,以及全球存储市场对高性能内存的需求激增,使得这场技术竞赛愈发白热化。

三星的“双线并进”战略

三星此次第七代DRAM的研发路径呈现出“双线并进”的特点。根据公开信息,其第七代DRAM将基于10纳米级制程(D1d),并计划于2026年实现量产。值得注意的是,这一时间表与其第六代(1c)DRAM的量产计划(2025年)高度重叠。这种“研发-测试-量产”的并行推进模式,凸显了三星在技术迭代速度上的野心。

在具体实施层面,三星正在平泽P2工厂建设第七代DRAM试验线,同时计划于2025年初在平泽第四工厂(P4)引入第六代DRAM生产设备。这种产能布局的深层逻辑在于:通过第六代技术的快速商业化积累资金与经验,为第七代技术的突破提供支撑。行业分析指出,三星在10纳米级制程上的工艺优势可使其生产成本比竞争对手低20%-30%,这一成本壁垒或将成为其技术代际跨越的重要保障。

差异化竞争路径

面对三星的强势推进,SK海力士与美光采取了差异化的技术策略。SK海力士已完成第六代DRAM(D1c)的开发,并于2024年8月对D1d工艺进行了可靠性评估。其战略核心在于将1c纳米工艺优先应用于下一代HBM4E产品,通过绑定高附加值的HBM市场维持竞争力。这种“以HBM反哺通用DRAM”的策略,与该公司2024年业绩发布会上强调的“投资聚焦HBM”方向高度一致。

美光则通过技术跳跃实现突破。尽管其在第五代DRAM节点上曾落后于三星,但2024年10月推出的“1γ”(伽马)制程DDR5样品,标志着其在D1c技术上的快速追赶。更值得注意的是,美光通过将第五代(1β)与第六代(1γ)技术并行开发,成功缩短了与头部厂商的代际差距。这种“跨代融合”策略,使其在服务器DRAM市场获得了显著份额提升。

三星此次技术跃进并非孤立事件,而是系统性战略调整的组成部分。2024年底,三星DS部门负责人Jeon Young-hyun主导的电路重新设计计划,揭示了其技术优化的深度。具体而言,三星正在对第四代DRAM(D1a)的电路架构进行部分重构,旨在提升HBM产品的良率与性能。这一调整的直接目标是:在2027年实现亚10纳米级DRAM(D0a)的量产,从而在制程精度上拉开与竞争对手的差距。

产能结构调整同样关键。三星已明确停止10纳米(1z)工艺的LPDDR4 8Gb芯片生产,将资源集中于先进制程。这种“断尾求生”式的产能优化,反映出其对技术代际切换的决心。据产业链消息,三星第七代DRAM的测试线建设与第六代量产准备同步推进,预计2025年Q3前完成关键设备调试。

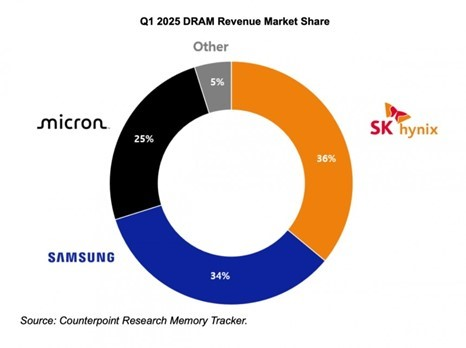

这场技术竞赛的深层影响已开始显现。在HBM领域,三星通过将1c DRAM优先应用于HBM4的策略,直接挑战SK海力士的市场主导地位。而美光的1γ DDR5样品出货,则加速了DDR5在服务器市场的渗透速度。三方的技术路线分化,正在重塑DRAM市场的竞争维度:三星聚焦制程领先性,SK海力士强化HBM绑定,美光则通过跨代技术实现差异化。

从供应链角度看,2025年将成为关键转折点。三星第六代DRAM的量产将加剧10纳米级市场的价格竞争,而第七代技术的试验线投产则可能引发设备厂商的订单争夺战。据SEMI数据显示,2025年全球半导体设备市场规模预计突破1200亿美元,其中存储领域占比将提升至35%。这种资本密集型的投入模式,将进一步抬高行业进入壁垒。

随着三星第七代DRAM量产计划的推进,全球存储市场正进入“技术代际+应用场景”双轮驱动的新阶段。从技术维度看,10纳米级制程的突破将重新定义DRAM的性能边界;从应用维度看,HBM与AI服务器的深度绑定、DDR5在数据中心的普及,正在创造新的增长极。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。