闪存,是如何工作的?

闪存使用网格中的浮栅晶体管存储数据。写入过程中,电子通过量子隧穿效应被捕获,从而改变单元电压。擦除操作使用块级电压脉冲重置电荷。由于绝缘氧化层的存在,数据即使在断电的情况下也能保存,但反复写入会降低单元的性能。

浮栅晶体管如何存储数据?

浮栅将电子捕获在氧化层之间,从而改变晶体管的阈值电压。这种二进制状态 (0/1) 通过感测电流来读取。与 DRAM 不同,电荷无需刷新周期即可保持完整。

每个闪存单元的核心都是一个 MOSFET,它带有一个夹在控制栅极和基板之间的附加浮栅。编程时,高电压 (15-20V) 迫使电子通过Fowler-Nordheim 隧穿效应穿过隧道氧化物。这些被捕获的电子会提高晶体管的阈值电压,该电压可在读取过程中检测到。实际上,这就像往水桶(浮栅)里注水,除非强行倒空,否则水不会漏。现代 3D NAND 将单元垂直堆叠,并使用电荷捕获闪存 (CTF)来减少电子泄漏。但是,如果氧化物降解会发生什么?就像生锈的管道一样,损坏的绝缘层会导致电荷泄漏,从而导致数据损坏。制造商使用纠错码 (ECC)和更严格的电压裕度来解决这个问题。

NAND 和 NOR 闪存架构有什么区别?

NOR 闪存使用并行单元进行随机访问,非常适合固件。NAND闪存将单元串联排列以实现高密度存储,优先考虑写入/擦除速度而不是直接寻址。

NOR 的并行结构允许字节级读取,使其行为类似于传统 RAM,但具有非易失性。但是,擦除块很大(64-128KB),写入速度很慢。相反,NAND 将 32-64 个晶体管串联起来,从而实现页面级操作(4-16KB)和更便宜的高密度设计。可以将 NOR 想象成一个图书馆,您可以在其中直接获取任何书籍(字节),而 NAND 则是一条传送带 — — 您必须一次处理整个盒子(页面)。从技术上讲,由于单元结构更简单,NAND 实现了更高的耐用性(100K 次,而 NOR 为 10K)。对于 SSD,制造商更喜欢3D TLC NAND,因为它具有每 GB 成本优势,尽管写入速度较慢。一个关键的权衡:NOR 的延迟是微秒,而 NAND 的随机访问延迟为毫秒。

数据写入和擦除操作是如何进行的?

写入操作通过隧穿效应注入电子,而擦除操作则利用热载流子注入来释放电荷。两者都需要高压电路,从而随着时间的推移对氧化层施加应力。

在编程期间,电压差(控制栅极上为 7-10V,衬底上为 0V)会产生足够强的电场,将电子推过隧道氧化物。擦除时,需要施加20V 的衬底偏压,从而逆转这一过程,将电子拉回。但问题在于:擦除会影响整个块(256KB-4MB),而不是单个字节。为什么?因为在每个单元上施加如此高的电压需要不切实际的电路。打个比方:重新粉刷整面墙(块)比修补散落的砖块(字节)更容易。SSD 通过过度配置来减轻擦除开销——保留额外的单元以分散磨损。但是,过多的写入仍然会在氧化物中产生电子陷阱,从而永久性地提高单元的阈值电压。

纠错在闪存寿命中起什么作用?

ECC 算法可以检测/纠正由电荷泄漏或写入干扰引起的位错误。像LDPC这样的高级方案可以补偿老化单元带来的问题,但会增加延迟。

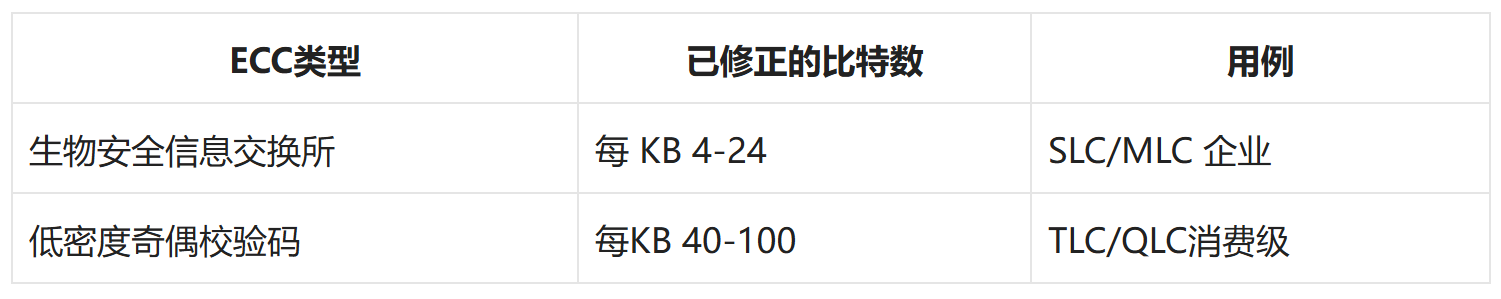

由于闪存单元要承受编程/擦除周期,因此氧化物磨损会增加误码率 (BER)。SLC(1 位/单元)可能使用基本BCH 码承受 10 万次循环,而 TLC(3 位/单元)需要强大的LDPC 码承受 10000 次循环。将 ECC 想象成数据的拼写检查 - 小错误会自动修复,但太多拼写错误则需要重写整个段落(数据重试)。从技术上讲,LDPC 使用概率模型来猜测原始电荷,但这需要更多的计算能力。禁用 ECC 以提高速度(例如,在 DIY SSD 项目中)可能会导致静默数据损坏。除了软件之外,跨芯片的RAID 式冗余等硬件技术也有帮助。你知道吗?QLC NAND 中 1% 的 BER 在 3 年后可能会激增至 25% - 因此消费级 SSD 通过积极的 ECC 来隐藏这一点。

磨损均衡如何延长闪存寿命?

损耗均衡技术利用固件映射将写入操作均匀分布到各个块。动态和静态方法可防止“热点”过早损坏单元。

闪存控制器通过逻辑到物理地址表跟踪每个块的擦除次数。动态损耗均衡将新写入重定向到较少使用的块,而静态损耗均衡则定期移动陈旧数据。这就像汽车轮胎的旋转一样——均匀的磨损可以最大化总里程。例如,具有 3K 耐久性和 10% 过度配置的 1TB SSD 可以处理 3.3PB 的写入量,相当于 20 年内每天写入 45GB。但实际上,由于小规模随机写入导致的写入放大,控制器通常会更早出现故障。专业提示:使用TRIM 命令标记已删除的文件,让控制器在空闲时间预擦除块。但是,损耗均衡无法解决固有的单元性能退化问题——最终,所有 NAND 都会变得不可靠。

为什么闪存单元的性能会随着时间推移而下降?

反复的隧穿效应会对氧化层造成应力,形成阻碍电荷移动的电子陷阱。累积的损伤会导致漏电流增加,直至电池无法维持规定的电压水平。

每个编程/擦除周期都会在二氧化硅晶格中产生缺陷。最初,ECC 会掩盖这些错误,但最终陷阱会累积,使单元变得“粘滞”——它们要么无法完全充电(编程干扰),要么泄漏太快(数据保留失败)。可以把它想象成花园水管:细小的裂缝会导致小泄漏(可纠正错误),但完全破裂则需要更换(坏块)。从技术上讲,磨损的 QLC 中的数据保留时间会从 10 年(新的 SLC)下降到数月。高温环境会加速这一过程——数据中心会主动将 SSD 冷却至 15°C 以下。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。