再登《自然》主刊!复旦团队研制“破晓”皮秒闪存

复旦大学集成芯片与系统全国重点实验室、芯片与系统前沿技术研究院周鹏-刘春森团队通过构建准二维泊松模型,在理论上预测了超注入现象,打破了现有存储速度的理论极限,研制“破晓(PoX)”皮秒闪存器件,其擦写速度可提升至亚1纳秒(400皮秒),相当于每秒可执行25亿次操作,是迄今为止世界上最快的半导体电荷存储技术。

相关成果以《亚纳秒超注入闪存》(Subnanosecond flash memory enabled by 2D-enhanced hot-carrier injection)为题,于北京时间4月16日晚间在《自然》(Nature)期刊上发表

颠覆现有存储架构,跑进亚纳秒级速度大关

AI时代,大数据的高速存储至关重要。如何突破信息存储速度极限,一直是集成电路领域最核心的基础性问题之一,也是制约AI算力上限的关键技术瓶颈。要实现大数据的高速存储,意味着与之匹配的存储器必须是在存储速度、能耗、容量上均表现优异的“六边形战士”。

然而,既有存储器的速度分级架构形如一座金字塔——位于塔上层的易失性存储器(如SRAM、DRAM)拥有纳秒级的高速存储,但其存储容量小、功耗大、制造成本高、断电后数据会丢失;而位于塔底的非易失性存储器(如闪存)则恰恰相反,虽克服了前者的种种劣势,但唯一的美中不足,便是百微秒级的存取速度不及前者十万分之一,遑论满足AI的计算需求。

既然闪存除了速度都是优点,有没有可能补齐它的速度短板?为此,周鹏-刘春森团队开展攻关,试图重新定义存储的边界,找到一种“完美”的存储器。

作为闪存的基本存储单元,浮栅晶体管由源极、漏极和栅极所组成。当电子从源极顺着沟道“跑”向漏极的过程中,按下栅极这一“开关”,电子便可被拽入浮栅存储层,实现信息存储。

“过去为闪存提速的思路,是让电子在跑道上先热身加速一段时间,等具备了高能量再按下开关。”刘春森形象解释。但在传统理论机制下,电子的“助跑”距离长、提速慢,半导体特殊的电场分布也决定了电子加速存在理论上限,令闪存存储速度无法突破注入极值点。

从存储器件的底层理论机制出发,团队提出了一条全新的提速思路——通过结合二维狄拉克能带结构与弹道输运特性,调制二维沟道的高斯长度,从而实现沟道电荷向浮栅存储层的超注入。在超注入机制下,电子无需“助跑”就可以直接提至高速,而且可以无限注入,不再受注入极值点的限制。通过构建准二维泊松模型,团队成功在理论上预测了超注入现象,据此研制的皮秒闪存器件的擦写速度闯入亚1纳秒大关(400皮秒),相当于每秒可执行25亿次操作,性能超越同技术节点下世界最快的易失性存储SRAM技术。

这是迄今为止世界上最快的半导体电荷存储技术,实现了存储、计算速度相当,在完成规模化集成后有望彻底颠覆现有的存储器架构。在该技术基础上,未来的个人电脑将不存在内存和外存的概念,无需分层存储,还能实现AI大模型的本地部署。

十年磨一剑,做重要领域的底层理论创新

给技术取名为“破晓”,寓意打破既有存储速度分级架构,迎接一个全新的存储时代。朝着这一目标,团队聚焦闪存技术的速度问题,由浅入深研究长达十年。

2015年,复旦硕士在读的刘春森在导师周鹏指导下开展的第一项研究就是闪存器件。他们深知,面对高筑的技术壁垒,若想在闪存这一卡脖子领域取得重大突破,唯有另辟蹊径、持续创新。

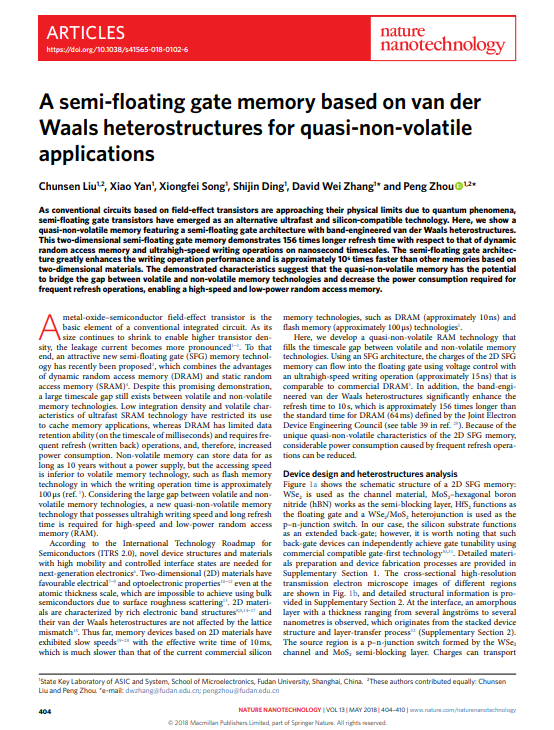

2018年,团队利用多重二维材料构建二维半浮栅闪存结构,将存取速度提升至10纳秒量级,这也是他们发表在纳米技术领域国际期刊Nature Nanotechnology上的第一篇闪存技术相关成果。不过,这项技术的器件结构仍较复杂,断电后,数据也只能保存十秒左右。

2018年 Nature Nanotechnology

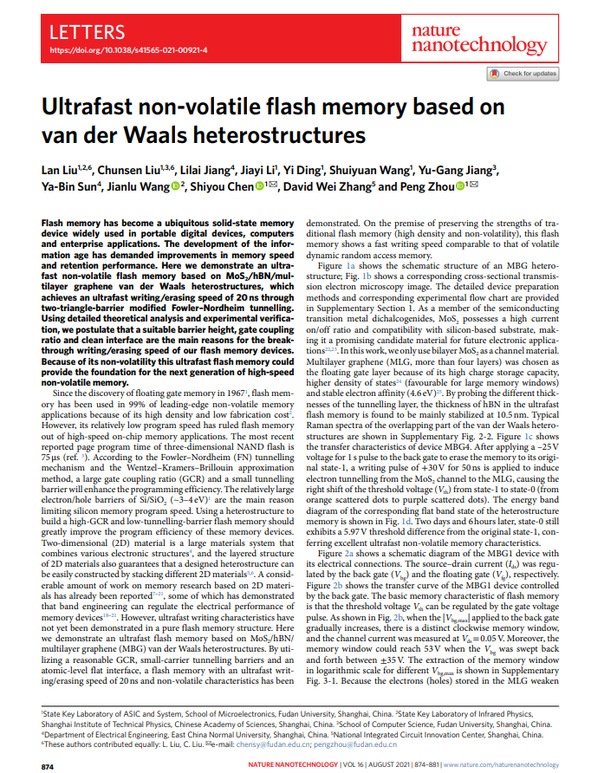

2021年,他们尝试修正传统理论机制。基于FN隧穿这一闪存工作机制,团队首次发现了双三角隧穿势垒超快电荷存储机理,并研制出范德华异质结闪存,将存储速度提至20纳秒的同时确保了数据存储的非易失(数据保存可达10年),成果再登Nature Nanotechnology。

2021年 Nature Nanotechnology

但这两项成果与团队期待的颠覆性创新仍有一定差距。时至今日,刘春森还时常会翻出1967年施敏博士(Simon Sze)和江大原(Dawon Kahng)在美国贝尔实验室提出浮栅晶体管概念所发表的论文,反复阅读这篇为闪存技术奠基的经典之作。

“60年过去了,如果还是沿着传统理论,或者靠换材料碰运气,很难做出颠覆性成果。我们一直在思考,能不能致敬前辈提出一个全新的闪存工作机制?”刘春森说。

于是,团队决心从底层理论机制着手创新。2021年底,他们基于高斯定理进行理论创新有了初步把握,最终在2024年构建起了准二维泊松模型,经过测试验证,迎来最终的“破晓”时刻。

回想自己如何从早期研究领域的多线并行转变为专注于闪存技术研究,刘春森觉得:“当你意识到什么是真正有价值的东西的时候,你就要开始聚焦,一头扎到底。”

“双腿”并行推动原型器件集成落地

衔接起实验室成果与产业化需求,确保理论创新与应用转化能够“双腿并行”,是周鹏-刘春森团队在研究中相互交织的两条主线。

“过去讲究理论创新,可能挖一个坑又换一个。如果你不往下多挖一步,把原型器件做到集成,产业界也不会接手完成这一步。”刘春森认为。

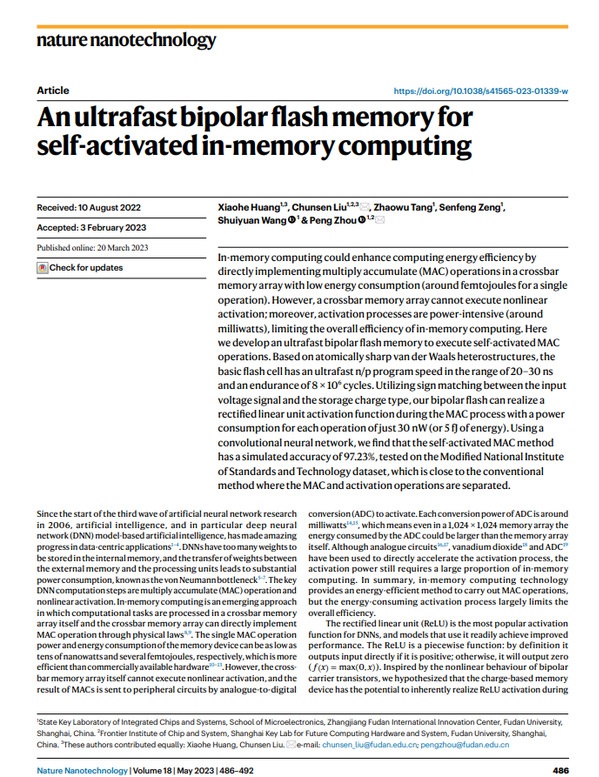

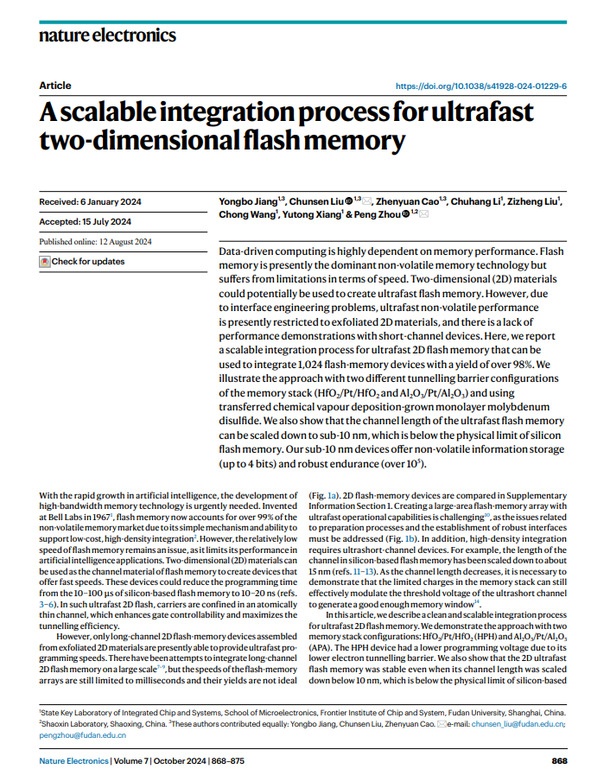

针对2021年的理论成果,团队在2023年发表的论文中验证了修正后的理论在其他半导体材料的通用性,并在2024年实现了最大规模1Kb纳秒超快闪存阵列集成验证,成功研发出物理沟道尺寸8纳米的超快闪存器件。

2023年 Nature Nanotechnology

2024年 Nature Electronics

正是依托这些前期完成的集成工作,此次研发的亚纳秒级原型器件得以向产业化落地加速推进。团队将“破晓”与CMOS结合,以此打造出的Kb级芯片目前已成功流片。下一步,他们计划在3-5年将其集成到几十兆的水平,届时可授权给企业进行产业化。

作为智能时代的核心基座,存储技术的速度边界拓宽或将引发应用场景指数级的革新,并成为我国在人工智能、云计算、通信工程等相关领域实现技术引领的“底气”之一。这场突破极限的挑战,未完待续。

复旦大学集成芯片与系统全国重点实验室、芯片与系统前沿技术研究院刘春森研究员和微电子学院周鹏教授为论文通讯作者,刘春森研究员和博士生向昱桐、王宠为论文第一作者。研究工作得到了科技部重点研发计划、国家自然科学基金人才类项目、上海市基础研究特区计划、上海启明星等项目的资助,以及教育部创新平台的支持。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。